# DESIGN TECHNIQUES TO MITIGATE THE IMPACT OF PVT VARIATIONS IN NANOMETER CIRCUITS

ANDRÉS FELIPE AMAYA BELTRÁN

UNIVERSIDAD INDUSTRIAL DE SANTANDER FACULTAD DE INGENIERÍAS FISICOMECÁNICAS ESCUELA DE INGENIERÍA ELÉCTRICA, ELECTRÓNICA Y DE TELECOMUNICACIONES BUCARAMANGA 2020

# DESIGN TECHNIQUES TO MITIGATE THE IMPACT OF PVT VARIATIONS IN NANOMETER CIRCUITS

## ANDRÉS FELIPE AMAYA BELTRÁN

Trabajo de grado presentado para optar al título de Doctor en Ingeniería, área Ingeniería Electrónica

Director: ÉLKIM FELIPE ROA FUENTES INGENIERO ELECTRÓNICO. PhD.

UNIVERSIDAD INDUSTRIAL DE SANTANDER FACULTAD DE INGENIERÍAS FISICOMECÁNICAS ESCUELA DE INGENIERÍA ELÉCTRICA, ELECTRÓNICA Y DE TELECOMUNICACIONES BUCARAMANGA 2020

#### **Acknowledgments**

It is no possible to complete the road towards a Ph.D. without the help of many people. People such as my advisor, my friends, my co-workers at OnChip, my wife, and my daughter, contributed to building a step to accomplish this stage.

First, I would like to thank Prof. Elkim Roa, who has been my advisor and my colleague during these years. His guidance re-shaped the scope of this thesis and was crucial to achieving the best results.

Second, I would like to thank my friends and colleagues at OnChip. I want to thank Luis, Javier, and Héctor for their help in tunning-up each aspect of this work, and also for the non-technical conversations about great past stories. Also, I want to thank Ckristian for his massive help with the digital and programming aspects of each circuit. Moreover, I would like to thank Rolando, Juan Sebastian, Hansel, Wilmer, Juan Pablo, and all the OnChip members that contributed to complete this work.

Third, I want to thank Universidad Industrial de Santander for the economic support during the first years of this road, for the resources to tape-out and test each circuit, and for funding all the patent applications. Thanks to Prof. Rodolfo Villamizar for his support and guidance during the first years. Also, thanks to CERN and Prof. Hugo Hernandez for my first tape-out.

Finally, I want to thank my wife Mildred, who has been my right hand during all these years. She provided me enough motivation at the last stage to finish writing this thesis. Thanks for understanding when you had to go alone to bed in so many occasions. Thanks to my father Jesús (R.I.P) for his huge support; this work is specially dedicated to him. And thanks to Gabriela, my daughter, for

giving me a new reason to complete this road.

Dedicated to all the people that contributed to finish this work.

Specially dedicated to my father (R.I.P)

# CONTENT

| 1 Introduction                                                    | 21 |

|-------------------------------------------------------------------|----|

| 1.1 Key aspects on robut SoC design                               | 23 |

| 1.1.1 High-speed serial links                                     | 23 |

| 1.1.2 Digital-to-analog conversion in SoC                         | 24 |

| 1.1.3 Power supply regulation                                     | 25 |

| 1.2 Contributions                                                 | 25 |

| 1.3 Thesis overview                                               | 27 |

| 2 An Offset Reduction Technique for Dynamic Voltage Comparators   | 28 |

| 2 An Onset Reduction reclinique for Dynamic voltage Comparators   | 20 |

| 2.1 Introduction                                                  | 28 |

| 2.2 Common Approach for Offset Calibration in High Speed Links    | 29 |

| 2.3 Proposed Offset Reduction Technique                           | 35 |

| 2.3.1 Performance Description                                     | 36 |

| 2.4 Residual offset                                               | 38 |

| 2.5 Experimental Results for the proposed PORT sub-circuit        | 43 |

| 2.6 Summary                                                       | 44 |

| 3 On-chip eye diagram Measurement for Comparator Characterization | 45 |

|                                                                   | 70 |

| 3.1 Introduction                                                  | 45 |

| 3.2 Measurement Strategy                                          | 48 |

| 3.3 Circuit Implementation                                        | 54 |

| 3.4  | Experimental Results                                              | 57 |

|------|-------------------------------------------------------------------|----|

| 3.5  | Summary                                                           | 61 |

| 4    | A 12b 10MHz Capacitive Digital to Analog Converter                | 63 |

| 4.1  | Introduction                                                      | 63 |

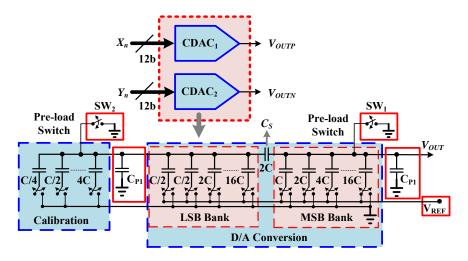

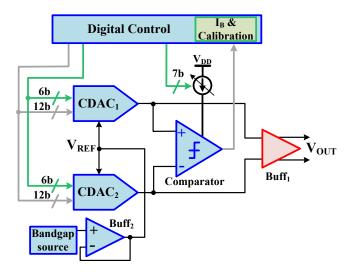

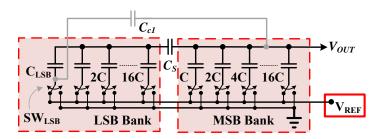

| 4.2  | Capacitive DAC topology                                           | 64 |

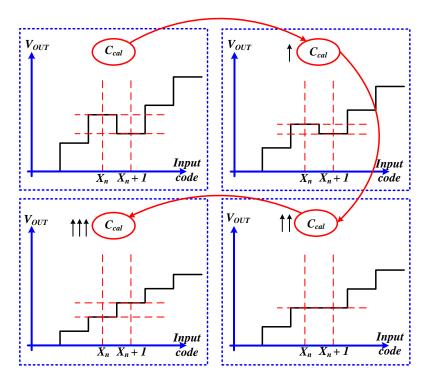

| 4.3  | Calibration and Trimming                                          | 67 |

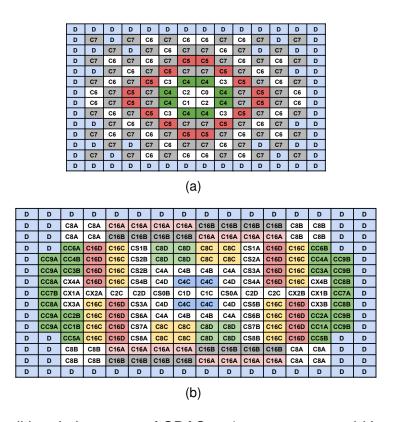

| 4.3. | 1 Layout                                                          | 70 |

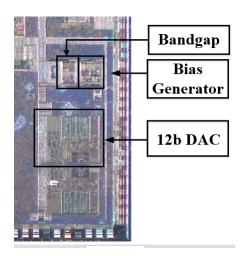

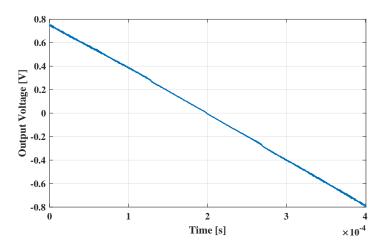

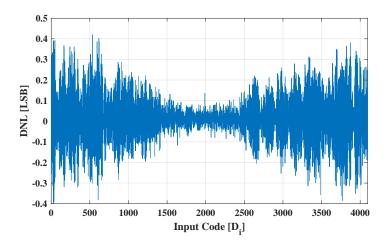

| 4.4  | Experimental Results                                              | 74 |

| 4.4. | 1 Debugging DAC performance                                       | 76 |

| 4.5  | Summary                                                           | 77 |

| 5 I  | mproving LDO Stability by Exploiting the Equivalent Series Resis- |    |

| t    | or of Compensation Capacitor                                      | 79 |

| 5.1  | Introduction                                                      | 79 |

| 5.2  | External Compensation of LDOs                                     | 81 |

| 5.3  | Adaptive Control of the LDO's Power Transistor                    | 86 |

| 5.4  | Experimental Results                                              | 89 |

| 5.5  | Summary                                                           | 92 |

| 6 (  | Conclusions                                                       | 94 |

| 6.1  | Conclusions                                                       | 94 |

| 6.2  | List of Publications                                              | 97 |

| 6.2. | 1 Conference papers                                               | 97 |

| 6.2. | 2 Journal papers in examination process                           | 98 |

| 6.2. | 3 Patents                                                         | 98 |

| 6.2. | 4 Patent requests                                                 | 98 |

| 6.2.        | 5 Other publications                                       | 98  |

|-------------|------------------------------------------------------------|-----|

| 6.3         | Future work                                                | 99  |

| BIB         | LIOGRAPHY                                                  | 101 |

| A I         | Process-Compatible DRAM Row-Hammering Mitigation Technique | 111 |

| <b>A.</b> 1 | Introduction                                               | 111 |

| A.2         | Pseudo-parallel Memory Cell Emulation                      | 112 |

| A.3         | On Deployability of a Weak-Cells-Based Monitoring System   | 114 |

| A.4         | Simulation Results                                         | 115 |

| A 5         | Conclusions                                                | 118 |

# LIST OF FIGURES

| 1  | Traditional RX front-end for high-speed interfaces: a) General Im-       |    |

|----|--------------------------------------------------------------------------|----|

|    | plementation; b) Calibration of sampler C; c) Calibration of sampler     |    |

|    | B. Only even (0°) phase components are only shown for explana-           |    |

|    | tion purposes                                                            | 30 |

| 2  | Traditional offset-correction scheme: Detailed circuit including switche | 3  |

|    | for commutation.                                                         | 32 |

| 3  | Alternatives implementations to reduce number of switches: a) use        |    |

|    | of Offset correction switches at each local summing point; b) turn-      |    |

|    | ing off of global summer                                                 | 33 |

| 4  | Power increment when using classical offset-correction techniques        |    |

|    | in high-speed signal interfaces: a) load Capacitance, b) bias current.   | 33 |

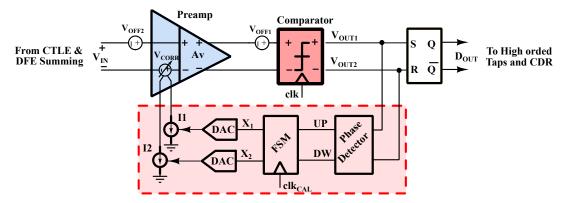

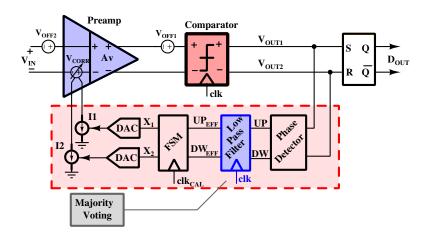

| 5  | Block diagram of the proposed offset reduction technique                 | 34 |

| 6  | Implemented phase and frequency detector                                 | 35 |

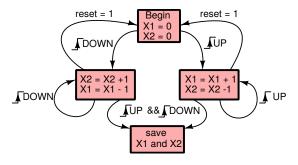

| 7  | State diagram of the FSM                                                 | 36 |

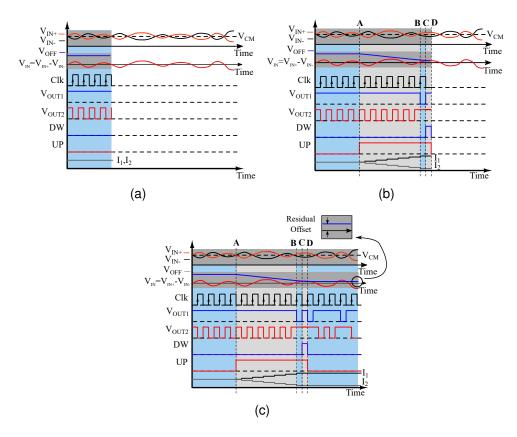

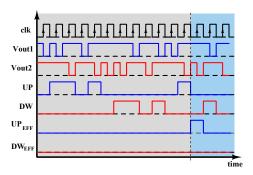

| 8  | Timing diagram of the proposed technique: a) saturated compara-          |    |

|    | tor due to large offset; b) calibration evolution and convergence; c)    |    |

|    | comparator calibrated                                                    | 37 |

| 9  | Block diagram of the proposed technique including a majority-voting      |    |

|    | block to perform a low-pass filter.                                      | 39 |

| 10 | Behavior description of a MJV filter                                     | 39 |

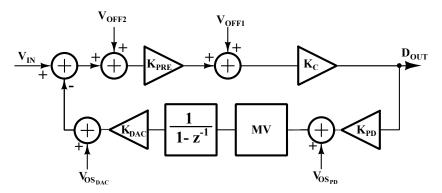

| 11 | Linear model of the calibration loop.                                | 40 |

|----|----------------------------------------------------------------------|----|

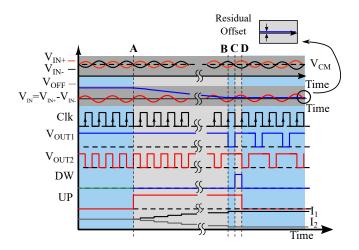

| 12 | Timing diagram of the proposed technique considering an uniform      |    |

|    | sequence (1010) for offset reduction when link tunning.              | 43 |

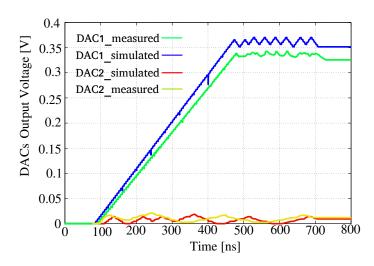

| 13 | Measured and simulated (TT) output voltage of calibration DACs       |    |

|    | during a calibration process                                         | 44 |

| 14 | Traditional high-speed serial link: use of equalizers at both TX and |    |

|    | RX sides.                                                            | 46 |

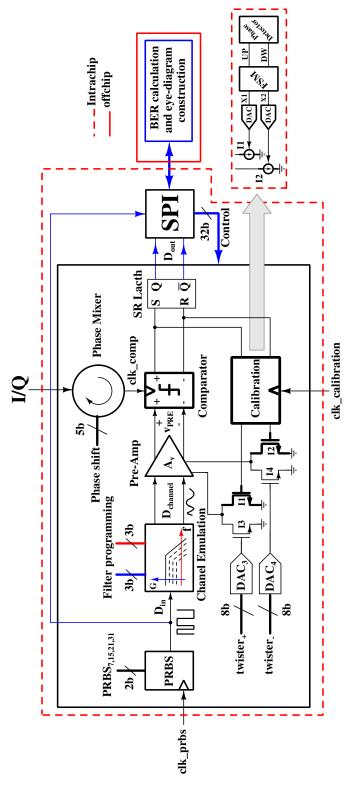

| 15 | System implemented for offset-reduction technique validation         | 49 |

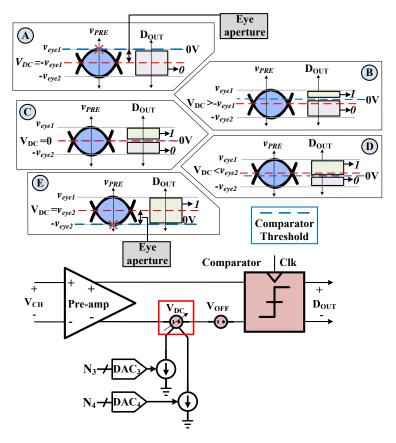

| 16 | Conceptual diagram of voltage shifting to build the eye diagram at   |    |

|    | the pre-amplifier output.                                            | 50 |

| 17 | Conceptual diagram of phase and voltage shifting to build the eye    |    |

|    | diagram at the pre-amplifier's output                                | 52 |

| 18 | Implemented sampling circuitry                                       | 54 |

| 19 | Implemented programmable Gm-C filter for channel emulation           | 54 |

| 20 | Nauta-OTA for Gm-stages implementation                               | 55 |

| 21 | Implemented Phase-Interpolator                                       | 55 |

| 22 | Testing board setup                                                  | 56 |

| 23 | Micro-photography of the proposed offset-correction technique        | 56 |

| 24 | Eye diagram at the pre-amplifier's output using the method de-       |    |

|    | scribed in section 3.2. The average value of each section was        |    |

|    | calculated using 50k samples of $D_{OUT}$                            | 57 |

| 25 | Measured on-chip eye diagram at the pre-amplifier's output using     |    |

|    | the method of section 3.2, and before offset calibration. The filter |    |

|    | attenuation is 26 dB and induced offset is: a)+44 mV, b) -56 mV      | 59 |

|    |                                                                      |    |

| 26 | Measured on-chip eye diagram after calibration for filter attenuation  |    |

|----|------------------------------------------------------------------------|----|

|    | of 26 dB                                                               | 59 |

| 27 | Measured on-chip eye diagram before calibration with 23 dB of at-      |    |

|    | tenuation and offset of a)+37 mV, b) -37 mV, c) Measurement after      |    |

|    | calibration.                                                           | 60 |

| 28 | Capacitive array used to implement D/A conversion.                     | 65 |

| 29 | Inclusion of parasitic components and calibration capacitors in DAC    |    |

|    | core                                                                   | 67 |

| 30 | Implemented DAC including calibration circuits and buffers             | 69 |

| 31 | Effect of $C_{cal}$ trimming on correction of quantization step        | 70 |

| 32 | Traditional placement of CDACs: a) common-centroid layout of a         |    |

|    | 80-bit binary-weighted DAC, b) layout of circuit from Fig. 29          | 71 |

| 33 | Placement of capacitors of implemented DAC (singled-ended array).      | 72 |

| 34 | Coupling capacitance in CDACs                                          | 73 |

| 35 | Microphotography of the designed DAC                                   | 73 |

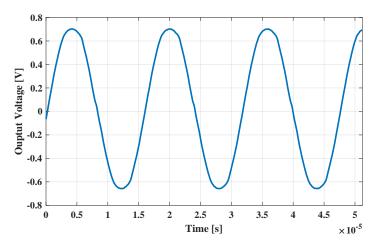

| 36 | DAC's differential output voltage.                                     | 74 |

| 37 | DAC's differential output voltage.                                     | 75 |

| 38 | DAC's differential output voltage: $F_s$ =10 MHz, $F_{signal}$ =78 KHz | 75 |

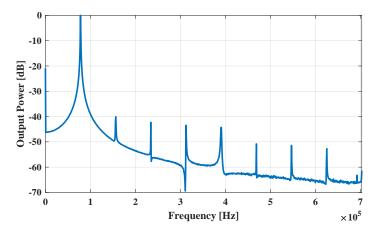

| 39 | Frequency spectrum of signal of Fig. 38                                | 75 |

| 40 | Traditional LDO topology based on a source-follower PMOS power         |    |

|    | transistor                                                             | 81 |

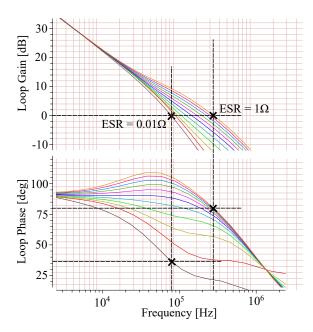

| 41 | Bandwidth improvement by ESR @ $I_L=20\mathrm{mA}$                     | 83 |

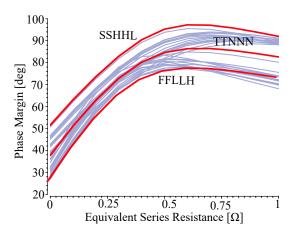

| 42 | Phase margin vs. ESR, including PVT variations @ $I_L=20\mathrm{mA}$   | 84 |

| 43 | Implementation of width and parasitic capacitance control of Power     |    |

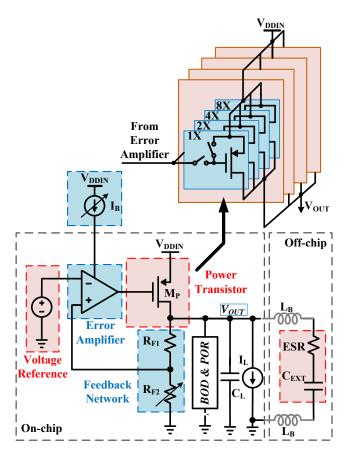

|    | MOSFET                                                                 | 85 |

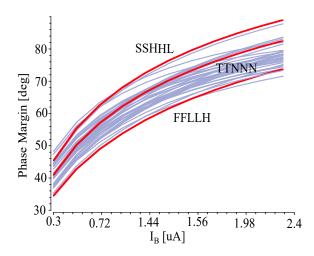

| 44 | Phase margin vs. bias current of the error amplifier, including PVT                           |              |

|----|-----------------------------------------------------------------------------------------------|--------------|

|    | variations @ $I_L=20\mathrm{mA}$                                                              | 86           |

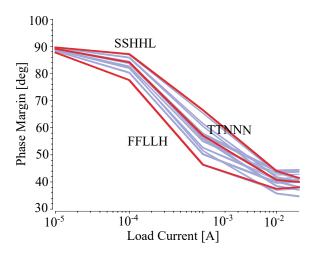

| 45 | Phase margin vs. load current without adaptive power transistor                               |              |

|    | control, and including PVT variations                                                         | 86           |

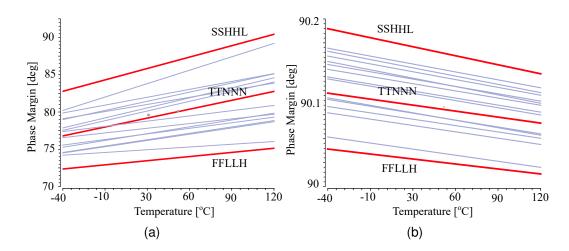

| 46 | Phase margin vs. Temperature with adaptive power transistor con-                              |              |

|    | trol and error amplifier biasing, and including PV variations: a) @                           |              |

|    | $I_L=20\mathrm{mA}$ b) @ $I_L=10\mu\mathrm{A}$                                                | 87           |

| 47 | BOD circuit for detection of LDO dynamics                                                     | 89           |

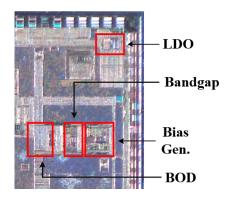

| 48 | Microphotography of the fabricated system highlighting the LDO,                               |              |

|    | the BOD and biasing circuitry.                                                                | 90           |

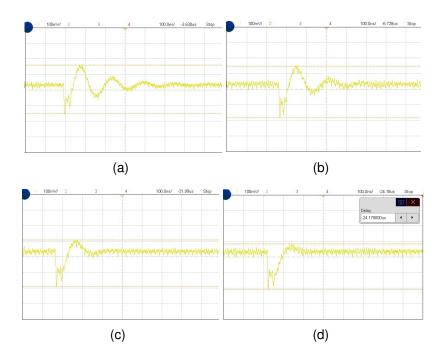

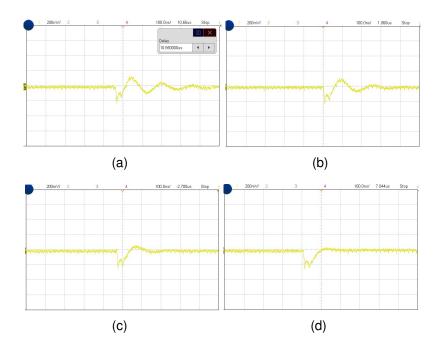

| 49 | Output voltage variation for a change in load current of 5 mA at                              |              |

|    | 27 °C and considering: a) Low-ESR b)ESR $\sim 1\Omega$ c)ESR $\sim 10\Omega$                  |              |

|    | d)ESR $\sim 20\Omega$ . Vertical scale is 100 mV/ $^2$ , $whilehorizontal scale is 100 mV/^2$ | $ns/^{2}$ 90 |

| 50 | Output voltage variation for a change in load current of 5 mA at                              |              |

|    | 125 °C and considering: a) Low-ESR b)ESR $\sim 1\Omega$ c)ESR $\sim 10\Omega$                 |              |

|    | d)ESR $\sim 20\Omega$ . Vertical scale is 200 mV/ $^2$ , $whilehorizontal scale is 100 mV/^2$ | $ns/^{2}$ 91 |

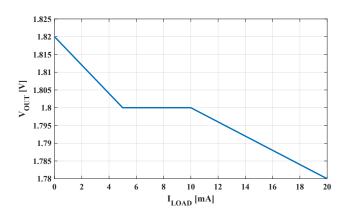

| 51 | Measured load regulation: Output voltage as a function of load cur-                           |              |

|    | rent                                                                                          | 92           |

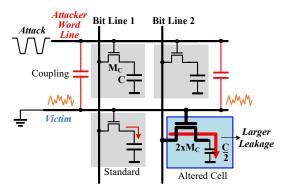

| 52 | Cell with increased leakage susceptibility using non-standard sized                           |              |

|    | cell                                                                                          | 113          |

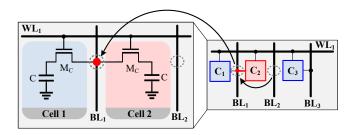

| 53 | Pseudo-parallel connection between two DRAM cells. Both cells                                 |              |

|    | share their bit line and word line, emulating a cell of twice the size                        |              |

|    | of a standard DRAM cell                                                                       | 113          |

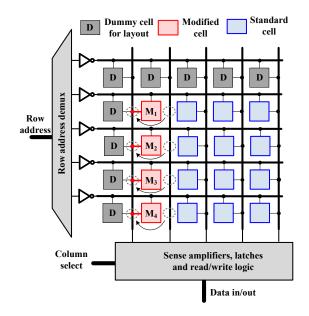

| 54 | DRAM array including the proposed monitoring system. Pseudo-        |

|----|---------------------------------------------------------------------|

|    | parallel cells consist of one modified cell and one dummy cell, ex- |

|    | ploiting the unusable bit of dummy cells                            |

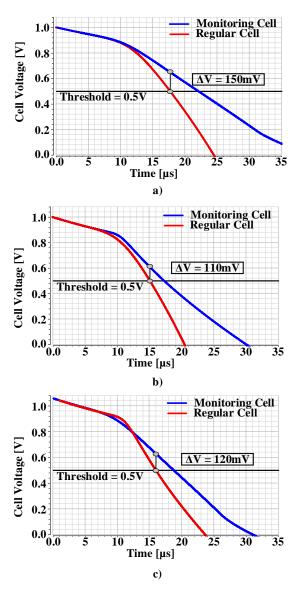

| 55 | Standard and monitoring cell voltage discharge including PVT vari-  |

|    | ations: a) Typical process corner and 50°C, b) Fast process corner  |

|    | and 125°C, c) Slow process corner and -40°C                         |

# LIST OF TABLES

| 1 | Comparison of the proposed technique with others works         | 62 |

|---|----------------------------------------------------------------|----|

| 2 | Performance summary of the designed DAC                        | 76 |

| 3 | Typical values for ESR of capacitors made of diverse materials | 84 |

| 4 | Performance summary of the designed LDO.                       | 92 |

## **List of Acronyms**

**PVT** Fabrication Process, Voltage and Temperature

SoC System on Chip

**PORT** Phase-based Offset Reduction Technique

**DFE** Decision Feedback Equalizer

**CTLE** Continuous Time Linear Equalizer

**PD** Phase Detector

FSM Finite State Machine

MJV Majority Voting

PRBS Pseudo-Random Bit Sequence

**BER** Bit Error Rate

**SPI** Serial Programmable Interface

**FPGA** Field Programmable Gate Array

**DAC** Digital to Analog Converter

**CDAC** Capacitive Digital to Analog Converter

**DNL** Differential Non-linearity

**INL** Integral Non-Linearity

**MSB** Most Significant Bit

LSB Less Significant Bit

**CMRR** Common Mode Rejection Ratio

**LDO** Low Drop-out Linear Regulator

**ESR** Equivalent Series Resistance

PM Phase Margin

**BOD** Brown-out Detector

**RESUMEN**

TÍTULO: TÉCNICAS DE DISEÑO PARA MITIGAR EL IMPACTO DE LAS VARIA-

CIONES PVT EN CIRCUITOS NANOMÉTRICOS \*

**AUTOR:** ANDRES FELIPE AMAYA BELTRAN †

PALABRAS CLAVES: Reducción de offset, variaciones PVT, calibración de DNL,

regulador de tensión, conversión de datos.

El impacto de las variaciones del proceso de fabricación, la temperatura de

operación y la tensión de alimentación (PVT) en el rendimiento de Systems-on-

Chip (SoC) generalmente se mitiga mediante algoritmos de calibración. Estos

algoritmos (ejecutados generalmente en segundo plano) utilizan datos de sen-

sors PVT para ajustar la operación a expensas de hardware adicional, latencia y

consumo de energía.

Este trabajo presenta tres técnicas de diseño novedosas y de baja compleji-

dad para reducir la incidencia de variaciones PVT globales, locales y aleatorias

en el rendimiento de un SoC. La primera alternativa aborda la calibración de

offset en ecualizadores de retroalimentación de decisión (DFE), utilizados en en-

laces seriales. El offset se detecta en el dominio de fase utilizando un detector

de fase en la salida del comparador. Esta detección permite eliminar la conexión

clásica de modo común en la entrada del comparador. El método permite la im-

\*Trabajo de Investigación.

<sup>†</sup>Facultad de Ingenierías Fisicomecánicas. Escuela de Ingenierías Eléctrica, Electrónica y de Telecomunicaciones. Director: Élkim Felipe Roa Fuentes.

17

plementación de una calibración sobre la marcha sin afectar la carga en la ruta de la señal.

La segunda técnica consiste en un algoritmo de calibración para ajustar la no linealidad diferencial (DNL) en convertidores digital-analógico capacitivo. El algoritmo reduce la necesidad de conectar la matriz capacitiva a Vcm mientras se calibra, lo que reduce la complejidad del circuito, la potencia y el consumo de área. La tercera técnica se concentra en mejorar la robustez de la estabilidad de los reguladores lineales. La estabilidad de frecuencia se ve mejorada por dos aspectos: un compensador de Adelanto-atraso, y un esquema adaptativo para la corriente de polarización y el tamaño del transistor de potencia. El compensador se implementa usando la resistencia en serie equivalente del capacitor externo. Además, una estimación de subimpulso realizada por el detector de brown-out de unidades de administración de energía convencionales establece la corriente de polarización y el tamaño del transistor de paso.

**ABSTRACT**

TITLE: DESIGN TECHNIQUES TO MITIGATE THE IMPACT OF PVT VARIA-

TIONS ON NANOMETER CIRCUITS 1

**AUTHOR:** ANDRES FELIPE AMAYA BELTRAN §

**KEYWORDS:** Offset reduction, PVT variations, DNL calibration, voltage regula-

tor, data conversion

The impact of variations of the fabrication process, operating temperature and

supply voltage (PVT) on the performance of Systems-on-Chip (SoC) is typically

mitigated using calibration algorithms. These algorithms (executed usually at the

background) use data from PVT sensors to adjust operation at expenses of ex-

tra hardware, latency, and power consumption. Even for mature technologies

(>100 nm), PVT sensing has a crucial role in complex SoC's aspects, such as

voltage regulation, data conversion and interface. Moreover, PVT sensors can

not sense the effect of local and random variations on the SoC performance.

Specifications such as offset (produced mainly by mismatch) requires the design

of dedicated calibrations procedures, increasing hardware overhead.

This work introduces three novel and low-overhead design techniques to re-

duce the incidence of global, local, and random PVT variations on SoC's per-

formance. The first alternative addresses offset calibration in decision feedback

<sup>‡</sup>Research Work.

§Facultad de Ingenierías Fisicomecánicas. Escuela de Ingenierías Eléctrica, Electrónica y de Telecomunicaciones. Advisor: Élkim Felipe Roa Fuentes.

19

equalizers (DFE), used in serial links. Offset is sensed in the phase domain using a phase detector at the comparator output. The phase-domain sensing allows eliminating the classical common-mode connection at the comparator's input. The method enables the implementation of an on-the-fly calibration without affecting the load at the signal path.

The second technique consists of a lightweight calibration algorithm to adjust differential non-linearity (DNL) in split-capacitors digital-to-analog converters. The algorithm reduces the necessity of connecting the capacitive array to Vcm while calibrating, thus reducing circuit complexity, power, and area consumption.

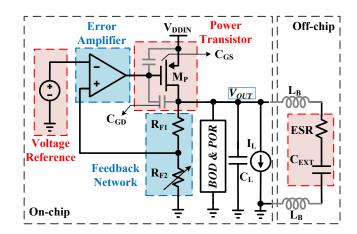

The third technique concentrates on improving the stability robustness of linear low-dropout regulators. Frequency stability is improved by two aspects: a lead-lag compensator, and an adaptive scheme for bias current and power transistor size. The compensator is implemented by exploiting the equivalent series resistor of the external capacitor. Also, an undershoot estimation made by the brown-out detector of conventional power management units sets bias current and pass transistor size.

#### 1. Introduction

The continuous scaling of CMOS technologies has allowed for the development of complex, high-performance systems-on-chip (SoCs). Typically, a SoC integrates into unique substrate functions such as volatile and non-volatile memory, multiple levels of data processing, I/O subsystems, and data conversion. Having these types of functions available in a single chip has been crucial to boosting the growth of both low-end and high-performance applications. The interconnection of everything to the internet (which constitutes the well-known internet-of-things (IoT) movement) is the most famous example of the importance of having the ability to read data from sensors, process it in the digital domain, and send it to the cloud, all in a single chip. Furthermore, the use of artificial intelligence to solve driving issues or facial recognition challenges is an example of how a high-performance SoC can deal with daily situations [1]. Even today's low-cost smartphones can perform 3D-video tasks due to the inclusion of hardware accelerators and high-speed links in the same chip.

As technology continues to reduce device dimensions, and as SoC complexity keeps growing, reliability has become one of the main design issues. This concern is related to guaranteeing that all the subsystems always perform according to the initial specifications. Reliability is also connected to being able to handle the effects of environmental changes on the performance, and with variations of any large scale production system. Optimal SoC design should include the ability to measure performance deviation and to make decisions about how to adjust small subsystems (or the whole application) to meet the intended throughput.

From the design point of view, a typical method to quantify the reliability of

a SoC is to evaluate its performance regarding variations of the fabrication process, operating temperature, and supply voltage (known as PVT variations). PVT variations consider a set of extreme operation conditions, with the purpose of evaluating possible worst-case situations that lead to malfunction or a reduced lifetime. PVT-oriented design guarantees circuit robustness against the uncertainty of physical parameters of silicon devices (always present in any mass-scale production line). Moreover, a PVT-aware design considers that a single SoC can be used in many environmental conditions. For instance, it is possible to find the same IoT SoC in both automotive (high temperature and corrosion environment) and human body movement applications (low temperature and stress).

A typical solution to reduce the impact of PVT variations is to use calibration circuits. This alternative tries to fix the circuit performance once it has been fabricated or during its operation. Calibration mainly occurs in the digital domain and involves a set of algorithms that compare an output and reference signal. Calibration adjusts parameters such as amplifier gain, bias signals, common-mode levels, or load capacitances to optimize performance.

Calibration is the most popular way to fix the performance of circuits such as data converters, analog and digital filters, instrumentation systems, and wireline transceivers. However, hardware overhead needed to perform this operation adds significant power consumption and silicon area, as well as an impact on the performance. Calibration involves the solution of optimization algorithms such as Least Mean Square (LMS) [2], requiring complex digital implementations. In some cases, such algorithms can demand more current than the main application, especially when calibration must be performed along normal operation of the system. Moreover, applications that include calibration circuits add additional costs related to verification and testing.

#### 1.1. Key aspects on robut SoC design

Some of the most critical aspects of any SoC are data transfer, data conversion, and power supply regulation. These three aspects involve the design of pure analog or mixed-signal circuits, whose robustness is lower compared with digital-only sub-systems. Digital circuits have the advantage of using transistors solely as switches, so the probability of having a functional failure is lower and depends on other subsystems such as power supply regulation [3, 4]. The following subsections detail the key aspects on adding robustness to a SoC design.

1.1.1. High-speed serial links Transfer of large amounts of data between integrated commercial devices is typical nowadays, as modern SoCs come readily equipped with high-speed interfaces such as USB 3.0 or Gigabit Ethernet ports [5,6]. Gigabit data rates are common due to the implementation of reconfigurable TX and RX blocks. These blocks can adapt circuit parameters according to the current transmission channel, as well as counter PVT variations. From the RX point-of-view, the maximum speed is strongly limited by equalization capability and by sampler sensitivity. Maximum equalization is a problem that has been solved mainly from a high-level perspective since equalizers are often treated as adaptable high-pass filters. However, sampler sensitivity is an issue strongly linked to PVT, especially for random or local process variations. Sensitivity gives a measure of the minimum signal amplitude that the RX block can sense, thus limiting channel attenuation and link speed. This specification is a function of transistor intrinsic gain, noise, and offset, the latter being caused by mismatch or intra-die variations. As a result, any SoC with a high-speed serial link must have an offset calibration routine, resulting in an increment of silicon area and power

consumption. Moreover, the SoC has to use part of its processing resources to execute the calibration algorithms, sometimes necessary even to stop data transmission.

1.1.2. Digital-to-analog conversion in SoC Digital-to-analog conversion is a crucial task when using a SoC for signal generation and audio applications. High-resolution DACs are present in many SoCs used in 3D-video and gaming platforms. SoCs are also used in feedback control systems and wireless applications which typically include medium and low-resolution converters. Despite the existence of several methods for D/A conversion, the capacitive topology is preferred over resistive and current-based methods. A capacitive DAC has reduced power consumption and noise level, and the matching of capacitors is better than the matching of resistors [7]. Moreover, a capacitive DAC can be integrated into many analog-to-digital converters, such as the successive-approximation-register (SAR) converter.

Linearity is the main issue when designing a robust DAC. Parasitic elements, produced by the layout pattern, strongly increase distortion. Furthermore, PVT variations impact dielectric properties, expanding the variation of unity and parasitic capacitance even more, and introducing offset. As a result, data conversion in SoC must include a calibration method that reduces the spread of quantization step throughout the dynamic range and for each digital input code. Calibration is often executed in the background, demanding a high additional computational load. In some cases, because capacitive DAC only consumes dynamic power, the execution in the background of calibration algorithms requires more power than the power delivered to the capacitors by the reference signal. The necessity of calibrating a converter in IoT applications has a high impact on lifetime and

final cost.

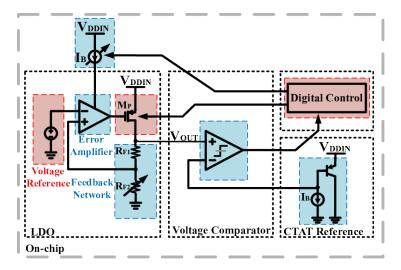

**1.1.3. Power supply regulation** Another essential subsystem in any SoC is the power-management unit (PMU). A PMU has the function of setting the required supply voltage for the other subsystems, according to operating speed and available energy. A PMU is typically composed of a switched conversion stage (DC-DC), followed by linear and low-dropout regulators (LDO). A DC-DC converter transforms (with high energy efficiency) the battery voltage into the standard level required by each subsystem. Given the switched nature of a DC-DC converter, its output presents a large ripple. That ripple is reduced by an LDO, which is a linear feedback amplifier with an output stage. Because an LDO has a feedback network, stability is the primary design concern. Open-loop gain and phase shift are a function of physical and electrical parameters of transistors, especially the intrinsic gain and parasitic capacitance of the power device. Therefore, PVT variations have a high impact on the performance, causing a weak and slow transient response, or a complete malfunction of other subsystems. A robust LDO must have a compensation strategy that counters PVT variations according to the load current and input voltage.

#### 1.2. Contributions

This thesis describes three low-complexity design techniques and circuit alternatives to mitigate the impact of PVT variations in circuits such as voltage comparators for decision feedback equalizers (DFE) in serial links, digital-to-analog converters (DAC), and low-dropout voltage regulators (LDO). For voltage comparators, the proposed circuit reduces offset without the traditional connection of both inputs to a common-mode voltage. For DACs, the design technique is fo-

cused on reducing the impact of parasitic capacitance on linearity. In the case of LDOs, the proposal is related to improving circuit stability through parasitic components of an external capacitor.

The contributions are summarized as follows:

- 1. A fully-digital, low hardware overhead offset reduction technique for dynamic voltage comparators. The technique senses offset in the phase domain using a classical phase-and-frequency detector, and can be applied to decision feedback equalizers in high-speed serial interfaces. In contrast to traditional methods, the proposed alternative does not require setting the comparator input to a common-mode voltage when calibrating offset, thus enabling the possibility of implementing an on-the-fly correction. Furthermore, a method for non-invasive eye-diagram construction was implemented for comparator characterization and validation of the proposed technique.

- 2. A low-complexity DNL calibration algorithm for split-capacitor based digital-to-analog converters, that does not require the use of an additional reference voltage ( $V_{CM}$  for instance) to measure and compensate DNL. Thus, it reduces circuit complexity and power consumption. The proposed algorithm is also tied to an analysis of the impact of traditional layout techniques on DAC linearity.

- 3. An alternative low-dropout regulator frequency compensation based on the implementation of a lead-lag compensator using equivalent-series-resistor (ESR) of external capacitor. In contrast to traditional methods, which implement additional circuits to eliminate the dependence regarding ESR, the proposed circuit takes advantage of the zero-pole pair at the LDO output to increase the phase margin. Moreover, a method for controlling the width of

the power-MOSFET and the bias current of the error-amplifier is discussed, based on the interaction between the LDO and the brown-out detector.

#### 1.3. Thesis overview

This document is organized as follows: chapter 2 describes a fully-digital, low complexity technique to compensate offset in voltage comparators that can be extended to decision feedback equalizers in high-speed serial links. Chapter 3 exposes a method to calculate an eye diagram for comparator characterization and without the need for external probes. Chapter 4 presents a low-hardware-overhead DNL calibration and some design considerations about the impact of using traditional common-centroid layout techniques on linearity. Chapter 5 shows how to use the parasitic equivalent-series-resistors (ESR) of a LDO compensation capacitor to improve robustness of frequency stability, and discusses the interaction of a brown-out detection circuit with bias current and power transistor setup. Finally, chapter 6 presents some conclusions about the results and recommendations for future works.

### 2. An Offset Reduction Technique for Dynamic Voltage Comparators

This chapter introduces a low-complexity technique to reduce the offset voltage of dynamic comparators used as samplers in decision feedback equalizers (DFE). The proposed method leverages an output-data all-digital phase estimation technique in which the comparator's input does not need to be set to common-mode voltage  $(V_{CM})$  during offset compensation. While traditional techniques might break the data link for offset adjustment, this work allows the comparator to be calibrated on the fly. This chapter explains the behaviour of the proposed technique, and validates its performance with preliminary simulations in a 180 nm node.

#### 2.1. Introduction

Offset reduction is one of the major concerns at the front-end of a high-speed wireline receivers. An offset-reduction technique has to be carefully chosen considering the additional circuit complexity and capacitive load penalty to the signal path. Comparators, used as samplers or slicers in decision feedback equalizers (DFE), face the challenge of sensing signals at data rates above 20 Gb/s with limited input signal swing. Considering the aggregated losses of low-pass channels, which can reach up to 40dB, signal amplitude at comparator input could be as low as 20 V [8]. As a result, comparator sensitivity specifications become limited by the accuracy of the offset correction scheme. Furthermore, any load added to the signal path to set up an offset-calibration scheme has a highly negative impact on signal amplitude and power consumption.

Traditional offset correction methods break the communication link to perform

calibration. A typical correction scheme sets the comparator input to a common-mode voltage  $(V_{CM})$  for offset sensing and compensation. This scheme requires the use of additional circuits (switches are often used for this task) to open the input signal path and connect the sampler input to  $V_{CM}$ . If the application demands an on-the-fly operation, it is inevitable that an extra signal path that processes input data will be included while calibration is executed. Therefore, extra circuitry must be added and consequently, capacitive load is increased, demanding more power and area consumption to meet timing specifications.

This thesis presents a novel scheme to reduce offset of dynamic comparators used in DFE circuits for high-speed interfaces. The chapter describes an integrated receiver scheme that implements the phase-domain offset reduction technique (PORT). Measurement results show its potential application for on-fly offset correction in high-speed link receivers. PORT works based on the output signal phase, presents a low complexity, and offers the possibility of a digital implementation without compromising speed and power. The main characteristic of PORT is the fact that calibration does not require setting the input of the comparator to a common-mode level, paving the way to eliminate the necessity of the alternative signal path.

This chapter is organized as follows: Section 2.2 shows common alternatives to compensate offset in DFEs; Section 2.3 describes PORT's operation principle and its circuit structure; Section 2.4 presents a residual offset analysis; and Sections 2.5 and 2.6 introduce experimental results and conclusions, respectively.

### 2.2. Common Approach for Offset Calibration in High Speed Links

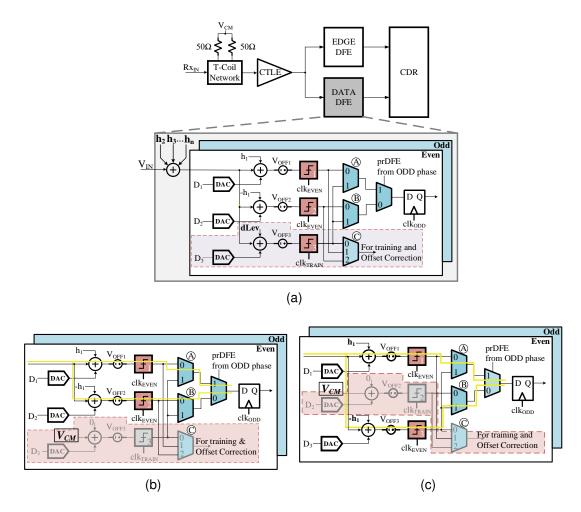

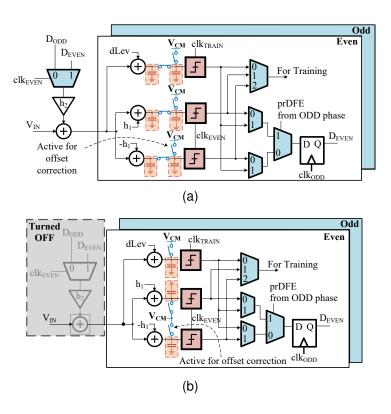

Fig. 1a shows a traditional double data rate (DDR) receiver front-end composed by a resistance termination (T-coil), a continuous time linear equalizer (CTLE),

Figure 1. Traditional RX front-end for high-speed interfaces: a) General Implementation; b) Calibration of sampler C; c) Calibration of sampler B. Only even (0°) phase components are only shown for explanation purposes.

two decision feedback equalizer for data and timing (edge) sampling respectively, and a clock and data recovery (CDR) block. The first tap of both data and edge equalizers uses a predictive or partial response implementation (prDFE) to meet timing requirements [9]. Commonly, a third sampler adapts equalizer coefficients, performs eye diagram monitoring, and is used for offset-correction purposes. During a tuning process, the third sampler extracts the error signal (dLev) required for the adaptation algorithm. The clock signal of the adaptive comparator ( $clk_{TRAIN}$ ) has a different phase compared to that of data samplers ( $clk_{EVEN}$  and  $clk_{ODD}$ ),

which is necessary for eye diagram monitoring during the normal operation [10].

The third comparator also allows performing an offset-calibration on a specific sampler while maintaining data transmission, in contrast to typical offset correction at the beginning of link operation [10]. Calibration of samplers only before beginning data transmission involves losing the option to track offset changes due to temperature and power supply (VT) variations during link operation. The inclusion of an on-the-fly calibration allows compensating samplers considering link variability due to VT variations. Figs. 1b and 1c present the traditional concept of on-the-fly calibration. In Fig. 1b the signal path (yellow line) includes samplers 1 and 2 as the prDFE section (red blocks), through the setup of multiplexers A and B. At the same time, offset-calibration is performed on sampler three (gray block) through multiplexer C and using a third DAC connected to the local summing point. A similar procedure is used to compensate offset of sampler 2, resulting in an equalizer formed by samplers 1 and 3, as Fig. 1c shows.

An on-the-fly offset-reduction on the samplers of Fig. 1 implies that during calibration each comparator input has to be disconnected from the signal path  $(V_{IN})$  and connected to a common-mode voltage  $V_{CM}$ , as presented by Figs. 1b and 1c [11]. Sampler input swapping is done by switches at the input of each path, as Fig. 2 shows. In Fig. 2 calibration is done on the third sampler, needing its input connected to  $V_{CM}$ . Furthermore, comparators one and two equalize the input signal, so that their inputs are connected to the summing circuit.

The main problem with the topology of Fig 2 is the load added by switches and extra signal-paths, increasing total losses and degrading signal amplitude. Increased circuitry also affects power consumption and area. Fig. 3 shows two alternatives to reduce the number of switches. The circuit of Fig. 3a uses switches at the output of each local summer (summer of each prDFE section), thus reduc-

Figure 2. Traditional offset-correction scheme: Detailed circuit including switches for commutation.

ing the total load of the global summer. However, the method of Fig. 3a only reduces the comparator's offset, so that the offset of summer amplifiers still affects the performance. Implementation of Fig. 3b uses switches only at the samplers' input while turning off the summer that receives the signal from high-order taps. Load capacitance is cut to 50% of the original value at the cost of losing the capability to perform on-the-fly correction.

Furthermore, the works presented in [12–15] calibrate offset using digital algorithms at the back-end during regular operation, and offset sampling techniques based on setting  $V_{CM}$  at comparator input. Back-end routines increase complexity and thus area and power, while traditional offset sampling methods add loading to the signal path. Other alternatives, such as the one presented in [16], achieves a fully on-fly operation by doubling the number of samplers and multiplexers, thus increasing power.

Figure 3. Alternatives implementations to reduce number of switches: a) use of Offset correction switches at each local summing point; b) turning off of global summer.

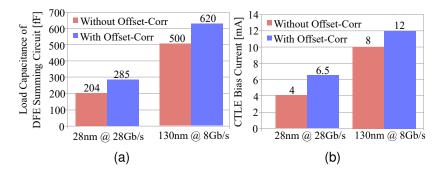

Figure 4. Power increment when using classical offset-correction techniques in high-speed signal interfaces: a) load Capacitance, b) bias current.

An alternative to overcome the aggregated losses due to the inclusion of extra signal paths and parasitic capacitance is to increase the peaking characteristic in the frequency response of previous equalization stages. An increment in equalization results in additional power consumption. Fig. 4 presents the simu-

Figure 5. Block diagram of the proposed offset reduction technique.

lated increment of load capacitance and bias current of DFE summing-circuit and continuous-time linear equalizers (CTLE) respectively. Those circuits are part of two different serial links: a 28 nm 28 Gbps DDR, and a 130 nm 8 Gbps using four quad-data-rate (QDR), with and without offset correction. For a 28 nm technology, the input and output capacitance of a complementary switch corresponds to 20% of the total load. Furthermore, the parasitic component increases up to 30% when including routing and interconnection paths.

In order to guarantee that CTLE+DFE-summing achieves the required bandwidth and equalization gain with the additional load, it is necessary to increase the CTLE bias current (and thus circuit dimensions) by more than 50%. This increment strongly impacts overall power consumption. Similar behavior is presented in the 8Gbps link implemented with a 130nm technology; capacitance increment is 25%, thus demanding 50% more of initial bias current.

By eliminating the necessity of connecting the input's sampler to  $V_{CM}$  for offset-correction, the power increment of Fig. 4 can be mitigated. Therefore, there is a need for an alternative way to measure offset that does not imply inserting switches at comparator input.

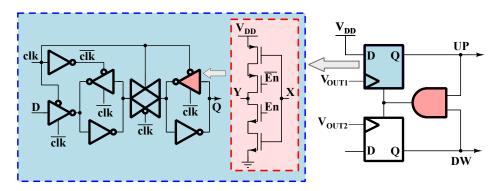

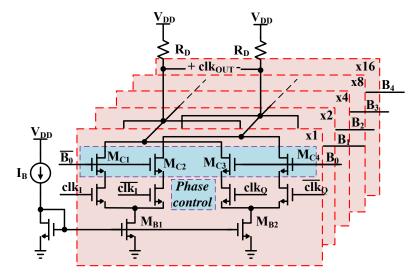

Figure 6. Implemented phase and frequency detector.

## 2.3. Proposed Offset Reduction Technique

Phase-domain Offset Reduction Technique (PORT) is a substitute to sense and compensate offset in dynamic voltage comparators with no need to connect their input to a common-mode voltage. PORT works by sensing comparator offset through the phase of its output signals, as shown in Fig. 5. Considering that the comparator is dynamic, its outputs change continuously between reset and comparison states, even if the input data is the same. Comparator outputs can be seen as two different oscillations, whose phase difference gives information about offset. The way to measure phase is by using a phase detector (PD) in a similar aspect as in a PLL. The PD senses the phase difference between  $V_{OUT1}$  and  $V_{OUT2}$ , whose output controls the transition of a finite-state-machine (FSM). Thus, the FSM outputs  $X_1$  and  $X_2$  set the bias current of a preamplifier. The correct adjustment of currents  $I_1$  and  $I_2$  reduces the offset introduced by the system, which is a combination of the offset of the comparator accumulated at the preamplifier.

A phase-detector and the FSM compose the core of PORT. Fig. 6 shows the PD structure, consisting of two D-type flip-flops and an AND gate at the output, a classical frequency-phase detector [17]. Flip-flops structure corresponds to a

Figure 7. State diagram of the FSM.

master-slave pass-gate topology, and the AND gate is implemented using standard static CMOS logic. The FSM consists of two 8 bits UP/DOWN counters, allowing a differential variation of  $X_1$  and  $X_2$ . Fig. 7 presents the state diagram of the FSM. Finally,  $X_1$  and  $X_2$  control to two DACs. One relevant aspect of the proposed technique is the fact that the calibration circuit can be synthesized using digital standard cells, which allows migration between different technology nodes.

**2.3.1. Performance Description** Fig. 8 illustrates the calibration process. The total input-referred offset at the preamplifier input without calibration (Fig. 5) is:

$$V_{OFF} = V_{off1}/A_v + V_{off2} \tag{1}$$

where  $A_v$  is the gain of the pre-amplifier, and  $V_{off1}$  and  $V_{off2}$  are the offset of the comparator and the pre-amp, respectively. Assuming an input sequence, as shown at the top of Fig. 8a, and a positive offset so that  $|V_{in}| < V_{OFF}$ , the comparator cannot differentiate between a logic one or zero at its input. Therefore, output  $V_{out1}$  is clamped to  $V_{DD}$ , and  $V_{out2}$  oscillates between  $V_{DD}$  and ground. The comparator's continuing phase change from reset to comparison causes  $V_{out2}$  to oscillate (Fig. 8a). The calibration circuit is turned on at point A of Fig. 8b, causing

Figure 8. Timing diagram of the proposed technique: a) saturated comparator due to large offset; b) calibration evolution and convergence; c) comparator calibrated

that, while the comparator is saturated, outputs UP and DW of the phase detector are always high and low, respectively. This behavior produces an increment in  $X_1$  while  $X_2$  decreases, producing a differential increment in bias currents  $I_1$  and  $I_2$  by means of the DACs. The change in bias currents eventually produces an additional offset  $V_{\rm CORR}$  in the opposite direction of  $V_{OFF}$ . If offset is negative, the behavior of UP and DOWN signals will be exchanged, as well as for  $X_1$  and  $X_2$ . A detailed implementation of each block in Fig. 5 is addressed in the next chapter.

If  $|V_{in}| > (V_{\text{CORR}} - V_{OFF})$  and the next logic zero reaches the input, the comparator output  $V_{out1}$  will go low (point B of Fig. 8b). Then, in the next rising edge of  $V_{out1}$  (point C) the DW signal will go high, causing the phase-detector to reset

(point D). Consequently, the increment of bias currents stops, exchanging  $V_{out1}$  and  $V_{out2}$  roles. Thus, the process can be restarted in the opposite direction, making bias currents oscillate around a new reached DC level (Fig. 8c). These final currents conditions are used as a stop criterion of the calibration process. Furthermore, Fig. 8c shows a half clock cycle as the duration of DW signal because the reset path of Fig. 6 includes delay stages to eliminate glitches.

The described behavior does not include setting the comparator input to a common-mode  $V_{CM}$  voltage, while calibration is carried out. Therefore, PORT avoids all switches at the input of each sampler of Fig. 2. Moreover, the feedback loop includes only an accumulator (the FSM) so that the system behaves as a one-dominant-pole one. Having only an accumulator allows a stable performance for a large range of bias currents and quantization steps, offering a large tolerance to PVT variations. The correct selection of  $I_{1,2}$  and DAC reference voltage creates a circuit behaving as a dominant pole system, whose phase margin is  $90^{\circ}$ . Additionally, because of the FSM is an Up/Down counter, PORT achieves a reduced convergence time because its critical path does not limit the settling time of bias currents. For that reason, calibration speed is limited only by the DACs.

#### 2.4. Residual offset

PORT can be summarized as follows: first, to apply a bit sequence at the slicer input; then, to measure the phase difference between sampler outputs to calculate offset; finally, to adjust preamplifier bias currents based on the phase-detector output and using the FSM and DACs. Considering the feedback loop formed by the calibration circuit, correction signal  $V_{CORR}$  tries to follow total input-referred offset  $V_{OFF}$ . Thus, residual offset  $V_{RES}$  (defined as  $V_{RES} = V_{OFF} - V_{CORR}$ ) gets

Figure 9. Block diagram of the proposed technique including a majority-voting block to perform a low-pass filter.

Figure 10. Behavior description of a MJV filter

lower as the technique converges. Reduction of  $V_{RES}$  leads to an improvement in the slicer's sensitivity, as offset is a key aspect for the minimum signal amplitude that a slicer can process. The instant the magnitude of the input signal is larger than residual offset at, i.e.,  $|V_{in}| > V_{RES}$ , gives the stop criteria, as Fig. 8c shows. This behavior does not imply the cancellation of  $V_{RES}$ . PORT tries to find an equilibrium point at which residual offset remains below input signal amplitude, so that offset does not slant the slicer decision.

In order to minimize residual offset, the circuit of Fig 5 can be modified in two different aspects. First, to insert a low pass filter (LPF) between the phase detector and the FSM, as Fig. 9 suggests. Second, the DC component of the

Figure 11. Linear model of the calibration loop.

input data has to be zero, i.e., the number of logic ones is equal to the number of zeros. The function of the filter is to extract any long-term DC level of the slicer's output so that the negative feedback can cancel it out. The filter also reduces the ripple of  $X_1$  and  $X_2$  signals, which is beneficial to achieve a more accurate offset cancellation.

The low pass filter can be implemented using a majority-voting (MJV) algorithm in the same way as in a clock-and-data recovery circuit (CDR) [18,19]. This type of filter uses N samples of UP and DOWN signals and a voting function to calculate its output. The chosen voting function is the average of UP and DOWN signals because of its simple hardware implementation. So, the filter will produce an effective UP  $(UP_{EFF})$  signal if the number of UP samples is larger than DOWN ones, and vice-versa  $(DW_{EFF})$ , as Fig. 10 shows. Using an MJV filter at the output of the phase detector avoids the use of multiplication blocks, which would be necessary when using a classical digital filter at the output of the FSM. Furthermore, the input signals of the MJV block are 1-bit long, in contrast with the 8-bit output of the FSM, resulting in a low hardware overhead and low impact on the critical path.

The main drawback of including a filter in the calibration loop is an increment

in convergence time. Even using a first-order, the extra pole might lead to stability issues. For that reason, the magnitude of the feedback currents and the DAC's reference voltage have to be selected so that the open-loop gain satisfies gain and phase margin requirements. A large bias current and DAC's quantization step lead to a large overshoot and non-linear behaviour at the pre-amplifier. Furthermore, a low open-loop gain results in a slow convergence. In this case, the lower the pole frequency of the filter, the higher the low-frequency feedback gain and thus the possibility to minimize the residual offset. However, stability becomes critical as the filter approaches an integrator.

The necessity of a DC balanced input can be explained using a linear model of the calibration circuit (Fig. 11). Gain blocks model the comparator and phase-detector. The output  $D_{OUT}$  is:

$$D_{OUT} = \frac{(V_{IN} + V_{OFF2} + V_{OS_{DAC}})K_{PRE} \cdot K_C (1 - z^{-1})}{K_{PD} \cdot K_{DAC} \cdot MV \cdot K_{PRE} \cdot K_C + 1 - z^{-1}} + \frac{V_{OFF1} \cdot K_C (1 - z^{-1}) + V_{OS_{PD}} \cdot MV \cdot K_{DAC} \cdot K_{PRE} \cdot K_C}{K_{PD} \cdot K_{DAC} \cdot MV \cdot K_C K_{PRE} + 1 - z^{-1}}$$

(2)

where  $K_C$ ,  $K_{PRE}$ ,  $K_{DAC}$  and  $K_{PD}$  represents the gain of comparator, preamplifier, DAC, and phase detector, respectively. MV is the gain of the majority voting block [19], the accumulator is related to the FSM,  $V_{OS_{DAC}}$  is the offset of DACs, and  $V_{OS_{PD}}$  corresponds to an equivalent offset caused by mismatch between the UP and DW paths of the phase detector. Equation 2 shows a high-pass behavior because of a zero at z=1, which is a consequence of the accumulator in the feedback path. To have a zero at z=1 implies that the calibration loop will attenuate any DC component of  $V_{in}$ , as well as signals  $V_{OFF1}$ ,  $V_{OFF2}$  and  $V_{OS_{DAC}}$ , once it is turned on and reaches a steady-state. In other words, the average

value of the output tends to be zero. The only offset contribution that still affects the output is  $V_{OS_{PD}}$ , which, however, is attenuated by  $K_{PD}$ .

When the calibration process finishes and the circuit changes to normal operation, the last value of the output of the FSM is stored, generating a constant signal  $V_{CORR}$  that is continuously subtracted from the input. Therefore, if the DC component of  $V_{IN}$  is zero while calibrating, it is possible to cancel the contribution of  $V_{OFF1}$  and  $V_{OFF2}$  during normal operation. If the input signal does not have an average null component while performing offset-correction,  $\overline{V_{IN}}$  will influence the calculation of the compensation signal  $V_{CORR}$ , i.e., the system process  $\overline{V_{IN}}$  as another offset source. For instance, if the input data corresponds to a bitstream generated by a 15th order pseudo-random bit sequence (PRBS), the number of logic ones occupies a 49.9% of the total sequence length (32 kb). So, the DC component, and thus the residual offset, is 61  $\mu$ V.

To have a DC balanced  $V_{IN}$  signal during offset calibration has the same effect as connecting the input signal to a common-mode voltage, which is the main advantage of the proposed technique. Considering that the transmitter of many high-speed standards has a scrambler (whose primary function is to reorganize the transmitted data to avoid undesired sequences such as a large number of consecutive logic ones (or zeros)), there is no need to include additional hardware to randomize data and reduce its average level.

A high-speed link also has to execute a training and calibration procedure before data transmission starts. In a training process, the transmitter and receiver communicate with each other mainly in order to tune equalization and clock-and-data recovery parameters. Therefore, a group of specific data sequences is produced at the transmitter to adjust DFE coefficients ( $h_{1,2...n}$ ) and CDR loop. Traditional training data sequences have a period composed of a logic one followed by

Figure 12. Timing diagram of the proposed technique considering an uniform sequence (1010...) for offset reduction when link tunning.

a zero, as Fig. 12 shows. This sequence has a zero DC value, so PORT is compatible with current training procedures without the need for additional hardware. Although offset-reduction is a process that has to be executed before equalization tuning (because equalization depends on the sampling precision of the input signal), the pattern shown in Fig. 12 does not require being equalized by the receiver because of its uniform transition from one to zero each clock period.

## 2.5. Experimental Results for the proposed PORT sub-circuit

Fig. 13 shows the measured DACs signals while the calibration process is performed. PORT was implemented in a 130 nm CMOS technology, using 1.2 V as supply voltage. DACs reach the steady state after 400 ns indicating that PORT has finished. In this test, the calibration loop does not include the low-pass filter (MJV filter) which results in a higher ripple at the DACs outputs. Fig. 13 shows the results for the typical-case simulation and measurements for one sample. A difference of 35 mV between the two signals indicates the influence of mismatch on the circuit. PORT's average current consumption is 550  $\mu$ A including DACs. It

Figure 13. Measured and simulated (TT) output voltage of calibration DACs during a calibration process.

is important to highlight that the calibration time could be reduced implementing a faster DAC. A detailed validation of the proposed technique will be presented in the next chapter.

# 2.6. Summary

In this chapter, a low hardware-overhead calibration technique for dynamic voltage comparators has been proposed and verified experimentally. The proposed technique uses output-data phase as a variable to measure offset. Relevant characteristics of the proposed technique include the possibility of avoid to set input of each comparator to  $V_{CM}$  while offset-calibration is performed. Furthermore, the proposed method tracks temperature and supply voltage variations influence over offset along data transfer. Finally, the calibration sub-circuit was fully synthesized, which allow to extend the technique to different fabrication process and applications.

## 3. On-chip eye diagram Measurement for Comparator Characterization

#### 3.1. Introduction

Maximum data rate that can be transmitted through a serial link is limited basically by intersymbol-interference (ISI). Crosstalk between channels and lanes (FEXT and NEXT losses), impedance mismatch, and dielectric and ohmic losses of channel are the main sources of ISI. While a differential implementation can reduce crosstalk, impedance mismatch can be minimized using digital trimming of both transmitter and receiver termination resistance. However, channel losses can only be compensated using equalization [20], [21].

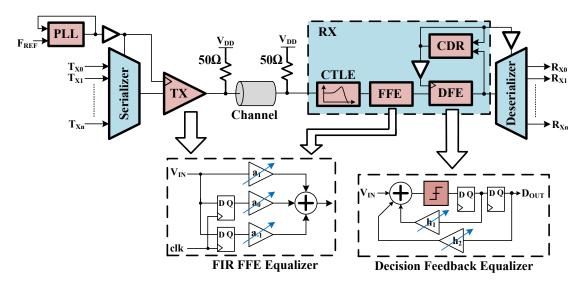

A high-speed link has a series of continuous and discrete time equalizers at both the transmitter and receiver blocks, as Fig. 14 shows. The transmitter block has mainly a discrete feed-forward FIR filter that implements pre-emphasis or de-emphasis equalization. Pre/de-emphasis produces a pre-distorted signal whose high-frequency components are boosted aiming to counter the low-pass characteristic of channels.

The receiver has typically a continuous-time linear equalizer (CTLE) and a decision feedback equalizer (DFE), with an additional feed-forward filter (FFE). A CTLE is characterized for its high-pass transfer function (with the same purpose as that of a TX filter), and can also attenuate low-frequency components to prevent over-equalization and saturation for short channels. A DFE is a non-linear mixed-signal equalizer whose main task is to mitigate post-cursor interference based on previous samples or symbols. A DFE is adequate for links with non-smooth or highly-dispersive channels. This type of equalizers can cancel ISI for

Figure 14. Traditional high-speed serial link: use of equalizers at both TX and RX sides.

15 or more unit intervals (UI) after the main cursor —where an UI is the period of one bit—. However, pre-cursor ISI can be reduced only by previous linear equalization which aims to modify the phase response of the link. Additional RX FFEs can work together with TX equalizers with the purpose of emulating a minimum-phase system, thus reducing pre-cursor ISI [22].

Combining all the characteristics of TX and RX equalizers it is possible to emulate the inverse channel's transfer function to minimize ISI. With a proper equalizer tuning according to the present channel it is possible to achieve ISI cancellation. Considering that equalizers can be modeled by a continuous or discrete transfer function, a crucial feature of a serial link is the ability to adjust each filter coefficients based on the channel. Equalizer adaptation is performed by specific training algorithms considering continuous or discrete filter characteristic. For CTLEs, training is based on power-spectral density measurements at the circuit's output. For DFEs and FFEs, the least-mean-square (LMS) and minimum-mean-square-error (MMSE) algorithms are executed respectively.

Once equalizer training is executed and data transmission begins, it is crucial to monitor continuously the link efficiency and its ability to adapt to different channel and operation conditions. The bit error rate (BER) is a common parameter for link characterization, which measures the number of wrong bits received, given a fixed transmitted bit-stream. Depending of the application the link will be used in, it must comply with an specific value of BER. For instance, USB 3.1 operating at 10 Gbps and PCle4 at 16 Gbps demand one wrong bit (1 error) for each 1000 Gb transmitted (BER =  $10^{-12}$ ). BER can be calculated using specific equipment such as BER analyzers, which include a series of data sources and checkers. A pseudo-random-binary-sequence (PRBS) generator is the main type of data stream because it can emulate a pseudo-random bitstream given a particular seed, that can be modeled deterministically [23]. Since a PRBS is a deterministic source, it is possible to implement a circuit that checks if the recovery data is correct or not, which is called a PRBS-checker.

The main issue with BER characterization is the fact that it is not possible to measure the number of wrong bits received when the link is transmitting real data. Information is considered as a completely random signal, so it is not possible to check if received bits are correct or not. Although an interface might have error correction algorithms, such as cyclic redundancy checker (CRC), error detection is done after a complete information package is received. As a consequence, BER is an specification that can be measured at link setup and before transmission of random information.

Given the restriction with BER calculation, eye diagrams become the main performance metric for high-speed interfaces during operation [24]. An eye diagram is a plot composed by the superposition of several transmitted or recovered bits taken during one UI. Traditional methods to get an eye diagram involve to

oversample input signal with an enough resolution so that it is possible to capture signal transitions from 0 to 1 and vice versa. Moreover, the oversampling ratio should be greater than 10X so that timing can be sensed correctly. An eye diagram allows to calculate parameters such as jitter tolerance and voltage sensitivity, which are crucial for determining maximum transfer speed given a channel.

One of the major drawbacks of measuring an eye diagram is the load imposed by the equipment connected to the circuit. High performance probes can add up to 100 fF, that can degrade link performance dramatically, and especially when transfer speed is close to technology node limit. Performing an external measurement involves to add buffers for driving pad, wire-bonding and external capacitance, thus increasing area and power consumption. Moreover, external load can affect rinsing and falling times of measured waveform, thus introducing asymmetry on the eye diagram. Furthermore, it is not always possible to have a high-speed oscilloscope when considering debugging of commercial applications.

This chapter addresses the design and implementation of a on-chip non-invasive method and system to measure an eye diagram for high-speed applications. Measurement is completely digital and does not require external probes on the signal path. The method was validated experimentally using a 130 nm high-speed analog front end. An eye diagram will be used to measure slicer offset and sensitivity, so that experimental results are focused on showing the effectiveness of PORT [25].

## 3.2. Measurement Strategy

An eye diagram can be calculated by means of the implemented system on silicon described in block diagram of Fig. 15. The eye diagram measurements are performed on-chip without needing external probes. A pseudo-random bitstream

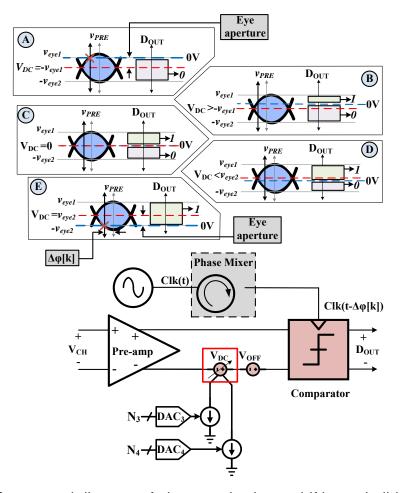

Figure 15. System implemented for offset-reduction technique validation.

Figure 16. Conceptual diagram of voltage shifting to build the eye diagram at the pre-amplifier output.

is sent through an emulated low-pass channel for recovering using the slicer. Testing system is composed by a programmable pseudo-random bit sequence (PRBS), a digitally-programmable low-pass filter, a digitally controlled phase-mixer, a strong-arm comparator with a current-controlled pre-amplifier, and an SPI interface. The PORT's core is on the feedback path of the comparator and, given its fully-digital implementation, it is possible to control its performance —and the operation of the others blocks—by the SPI.

The procedure of constructing an eye diagram can be explained as follows. The output signal of the pre-amplifier in Fig. 15 ( $v_{PRE}$ ), which is represented by the circuit of Fig. 16, is:

$$v_{PRE} = v_{AMP} \pm V_{DC}$$

with  $v_{AMP} = A_V \times v_{CH}$  (3)

where  $A_V$  is the pre-amplifier gain,  $v_{CH}$  is the output of the low-pass filter, and  $V_{DC}$  is a DC unbalance provoked by the difference between the two bias currents controlled by  $DAC_3$  and  $DAC_4$  (magnitude and sign). The larger the difference between  $I_{B1}$  and  $I_{B2}$ , the larger the unbalance at the pre-amp output. The inherent offset of low-pass filter and pre-amplifier also affect both  $v_{CH}$  and  $V_{DC}$  respectively. A DC unbalance at the pre-amplifier's output produces a vertical shift in  $V_{AMP}$ .

A voltage comparator, whose decision threshold is ideally zero, samples the pre-amplifier output. However, by using only one comparator, which performs as a 1-bit ADC, it is not possible to measure a full eye diagram aperture.

There are three different options to sample pre-amplifier's output with enough detail to measure eye diagram aperture: increasing the number of voltage comparators with different thresholds [26,27], varying the threshold of only one comparator, or shifting pre-amp output through  $V_{DC}$ . The first alternative implies a large power consumption because of the increased number of comparators performing as an ADC. This alternative is also not compatible with traditional DFE topologies. The second option is disadvantageous for high-speed operation because of the increased load at comparator input to produce a variable threshold.

The third alternative implies that the shift caused by  $V_{DC}$  displaces the upper and lower limit of  $v_{AMP}$  ( $v_{eye1}$  and  $v_{eye2}$ ) up to the comparator's threshold, as Fig. 16 shows. If  $|V_{DC}|$  is greater than  $v_{eye1}$ , so that  $v_{eye1} - V_{DC} < 0$ , the comparator's output is always 0 (frame A of Fig. 16); otherwise, when  $v_{eye1} - V_{DC} > 0$ ,  $D_{OUT}$  varies between 1 and 0 as a function of input data (frames B, C and D). The point

Figure 17. Conceptual diagram of phase and voltage shifting to build the eye diagram at the pre-amplifier's output.

where  $v_{eye1}$  is equal to the vertical displacement  $V_{DC}$  ( $v_{eye1}-V_{DC}=0$ ) sets the upper aperture of the eye diagram. Taking into account that  $V_{DC}$  can be set digitally using  $DAC_{3,4}$ , it is possible to have a digital representation of  $v_{eye1}$ . Following the same procedure,  $v_{eye2}$  can be measured by varying  $V_{DC}$  so that the lower aperture of eye diagram reaches the comparator threshold, i. e.  $v_{eye2}+V_{DC}=0$  (frame E).

To find out whether  $V_{DC}$  is lower or greater than the upper and lower apertures of  $v_{eye1}$  and  $v_{eye2}$  it is necessary to capture  $D_{OUT}$  and measure its mean value. When vertical displacement  $V_{DC}$  adjusts  $V_{amp}$  so that comparator's threshold is lower than  $v_{eye1}$  and greater than  $v_{eye2}$ , output data  $D_{OUT}$  coincides with a

recovered version of input data  $D_{in}$ . The data source is a PRBS generator whose mean value is 0 after all the sequence, i.e., produces the same number of symbols for ones and zeros. Hence, if  $D_{OUT}=D_{IN}$  the recovered data has the same statistical properties regarding input stream, and thus  $\mu_{D_{OUT}}$  is equal to 0 too:

$$\mu_{D_{OUT}} = \begin{cases} 0 & v_{eye1} \le V_{DC} \le v_{eye2} \\ -1 & V_{DC} < v_{eye2} \\ 1 & V_{DC} > v_{eye1} \end{cases}$$

(4)

If the mean value of  $D_{OUT}$  is equal to 0, the comparator can recover data and  $V_{DC}$  is bounded within an open region of the eye diagram. However, if the mean value is greater or lower than 0,  $V_{DC}$  corresponds to a closed region of the eye diagram. When a DC level is added to the pre-amplifier's output,  $D_{OUT}$  is slanted to 1 (and thus  $\mu=1$ ) if  $V_{DC}$  is larger than the maximum value of  $V_{eye1}$  and vice versa. Average value is calculated from a collection of 50k samples of  $D_{OUT}$  for each step of  $DAC_{3,4}$  digital words, which is adequate for a  $PRBS_7$  and  $PRBS_{15}$  sources (128b and 32kb length).

The horizontal aperture of the eye diagram at the pre-amplifier's output can be measured by performing the previous procedure given a phase difference between PRBS and comparator input clocks. Using a phase mixer it is possible to calculate vertical amplitude at different sampling instants, as Fig. 17 shows. A phase mixer can be configured digitally for four-quadrant operation, which adds the characteristic of shifting the comparator's clock along an entire unit interval. As a result, by combining vertical and horizontal displacement through  $DAC_{3,4}$  and phase-mixer respectively, it is possible to measure the eye diagram at the pre-amplifier's output without physical access.

Figure 18. Implemented sampling circuitry.

Figure 19. Implemented programmable Gm-C filter for channel emulation.

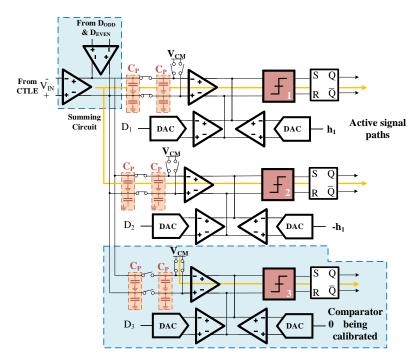

## 3.3. Circuit Implementation

The implementation of each building block of the scheme at Fig. 5 and Fig. 15 is based on classical structures as follows:

- Dynamic voltage comparator: This circuit is implemented using a strongarm topology [28]. The pre-amplifier is based on a degenerated commonsource circuit with active load (Fig. 18). Two current mirrors form its bias current for calibration and other two for twisting and eye diagram construction.

- PRBS: It is implemented using a shift-register counter with programmable

Figure 20. Nauta-OTA for Gm-stages implementation.

Figure 21. Implemented Phase-Interpolator.

word length, producing pseudo-random sequences based on 7th, 15th, 21th, and 31st order polynomials.

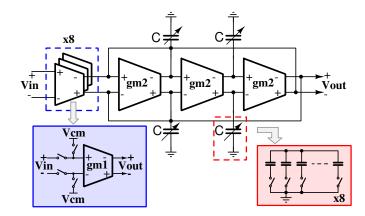

- Low-pass filter: The filter is emulating a channel, and corresponds to a

Gm-C topology. The gain and bandwidth can be controlled by varying the

number of input transconductors and the total capacitance of each node,

respectively (Fig. 19). Each transconductance stage was implemented using Nauta amplifiers, as in Fig. 20, due to their high bandwidth and rapid

prototyping by using digital standard-cells [29].

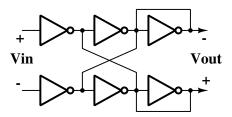

- Phase mixer: It corresponds to the well known analog phase interpolator that uses in-phase and quadrature input clock signals provided by an ex-

Figure 22. Testing board setup.

Figure 23. Micro-photography of the proposed offset-correction technique

ternal source (Fig. 21) to produce 32 different output phases (from  $0^{\circ}$  to  $360^{\circ}$ ) [30].

• DAC: We selected a classical R-2R 8-bit DAC to simplify the design [7].

Considering that the phase detector is connected directly to the output of the comparator, the additional load imposed by flip-flops (Fig. 6) could be critical in high-speed applications. A typical DFE structure uses a comparator to resolve 1-tap and 2-tap within 1 UI. Thus additional loading could degrade timing performance. However, a traditional 18T-flop only adds a load of about a 1X fanout of four (FO4) inverter.

Figure 24. Eye diagram at the pre-amplifier's output using the method described in section 3.2. The average value of each section was calculated using 50k samples of  $D_{OUT}$ .

## 3.4. Experimental Results

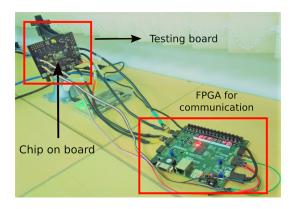

Experimental validation of PORT was achieved using the setup of Fig. 22. The testing board contains the fabricated circuit employing the chip-on-board technique. An FPGA was used to set up configuration registers and to extract data by communicating with the on-chip SPI interface.

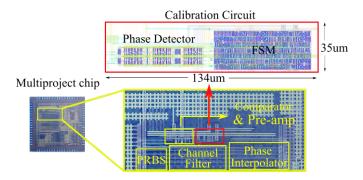

Fig. 23 presents the micro-photography of the implemented system, which was taped out in a CMOS 130 nm standard technology with a 1.2 V supply voltage to prove the concept. The dimensions of the calibration circuit are  $134 \, \mu \text{m} \times 35 \, \mu \text{m}$ . Both the phase detector and FSM are fully synthesizable, allowing migration between different technology nodes. Moreover, the FSM occupies  $55 \, \mu \text{m} \times 35 \, \mu \text{m}$ , and includes features such as variable output resolution for coarse and fine calibration and variation of feedback gain and convergence time, and sign controlling for negative feedback testing.

As a first test, the filter is configured to provide a 26dB attenuation at 800 Mbps, and the PRBS length is 15. As a consequence, filter output is 60mV since the

output signal of PRBS has an amplitude of 1.2 V (supply voltage). Although such data rate is lower than state-of-art serial links, filter configuration emulates the same attenuation that a common 3 meter cable for USB3.1@7 Gpbs has [31]. The main purpose of this prototype is to serve as a proof-of-concept for PORT.

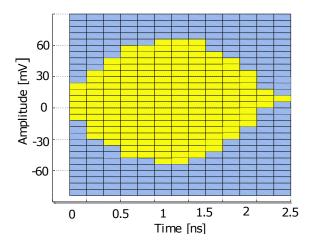

Figure 24 shows an eye diagram at the pre-amplifier's output using the methodology described in section 3.2. Data rate is 800Mbps (generated from a PRBS<sub>15</sub> source) and the filter is configured to have an attenuation of 26 dB. The yellow area corresponds to an open-region of the eye diagram because the average value of  $D_{OUT}$  is 0.5, thus implying that  $V_{DC}$  is bounded between  $-v_{eye2}$  and  $v_{eye1}$  (Fig. 16). The blue region refers to the closed region because the mean of  $D_{OUT}$  is different from 0.5.

The vertical amplitude of Fig. 24 is quantified based on the calculation of DC unbalance at the pre-amplifier's output and considering bias current of each transistor:

$$V_{DC} = \frac{1}{2} K_N \frac{W}{L} \left( V_{OV3}^2 - V_{OV4}^2 \right) R_D + V_{OFF1} + V_{OFF2}$$

$$= \frac{1}{2} K_N \frac{W}{L} \left[ \frac{4V_{REF}}{2^N} (2^{N_3} - 2^{N_4}) V_{OV3,4} \right] R_D + V_{OFF1} + V_{OFF2}$$

(5)

where  $V_{OFF1}$  is the offset of the comparator and  $V_{OFF2}$  the offset of the preamplifier. Furthermore,  $N_3$  and  $N_4$  are the digital words that control bias of twisting transistor, and  $V_{REF}$  is the reference voltage for both DACs.  $N_3$  and  $N_4$  are set to produce  $V_{REF}/2$  at DAC's output, and are varied differentially: first,  $N_3$  increases while  $N_4$  decreases for finding  $v_{eye2}$ ; then  $N_3$  decreases while  $N_4$  increases for measuring  $v_{eye1}$ . As a result, maximum and minimum value of yellow region is 65mV and 55mV respectively, implying an inherent offset of 5mV.

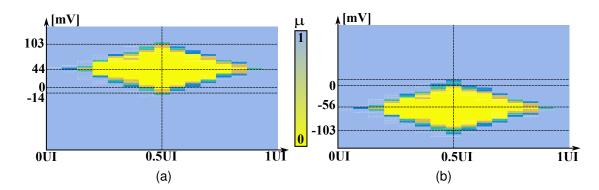

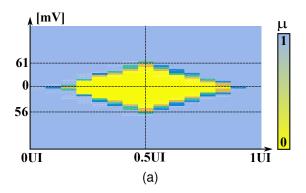

Figure 25a,b show the eye diagram at the input of the slicer without applying PORT. The input data also corresponds to a PRBS<sub>15</sub> source (32kb). This test

Figure 25. Measured on-chip eye diagram at the pre-amplifier's output using the method of section 3.2, and before offset calibration. The filter attenuation is 26 dB and induced offset is: a)+44 mV, b) -56 mV.

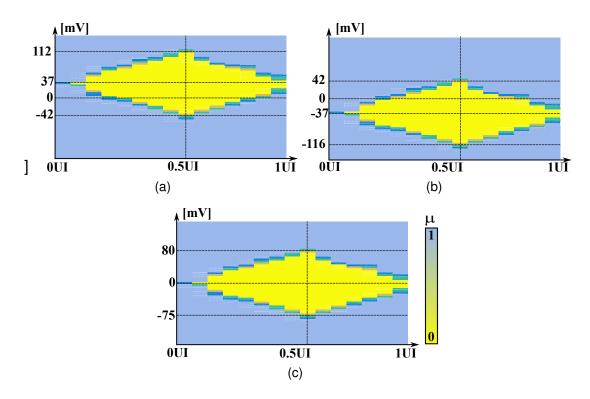

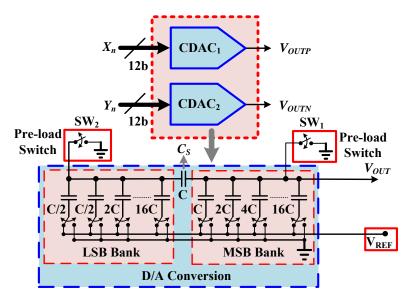

Figure 26. Measured on-chip eye diagram after calibration for filter attenuation of 26 dB.